Непрофессионально это советовать intel core вместо сервера

не профессионально балаболить основываясь на теоретических предположениях не основанных на фактах. + не имея реального опыта работы в том что обсираешь

Autumn

Autumn

не профессионально балаболить основываясь на теоретических предположениях не основанных на фактах. + не имея реального опыта работы в том что обсираешь

Коллега - профессионально, это про рекомендации проверенных решений, а не теоретические возможности новых интелов на очень ограниченном спектре материнок, с ограниченным спектром ОЗУ. Когда я получу готовые проверенные решения (а не надпись в руководстве асус о том что надо посмотреть проверенную память по списку асус, в котором найду 3 модели озу якобы работающие с определенными процами, а если не заведется - то ссзб, да еще противоречивые отзывы на формуах - у кого-то завелось, у кого-то нет), тогда я без проблем поддержку Вашу точку зрения. А пока я лучше поддержжу ну там кровавых HP-шников, которые не предлагают на новых корках 12/13ххх ЕСС память, а все равно вставляют зеоны. Буду работать по их схеме.

Autumn

Autumn

Теперь по существу, что бы не балаболить, вы мне реально предлагаете сэкномить 400-500 долл. и взять вместо связки:

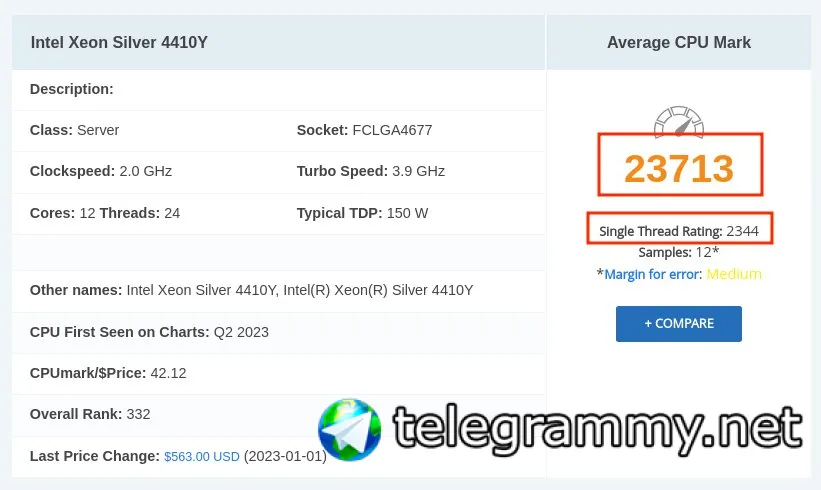

Intel Xeon Silver 4410Y 12C/24vC - 720$

Supermicro X13DEI - 1000$

1720$

наборчик из:

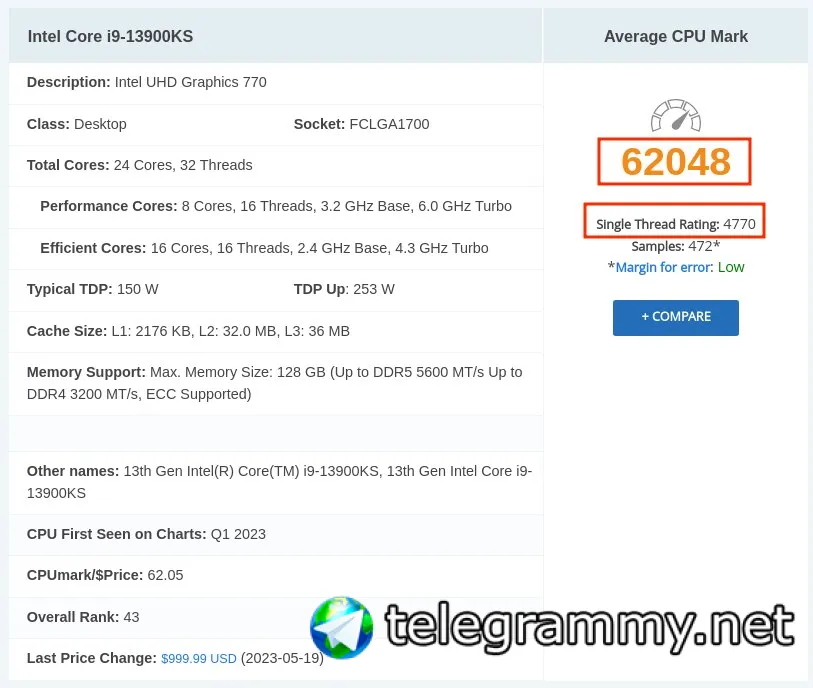

i9-13900KS 8P/16E/32vC - 887$

ASUS Pro WS W680-ACE IPMI - 410$

1300$

при этом сознательно урезать память с 8-и каналов до 2-х, ограничить максимальный объем ОЗУ с 4ТБ до 128ГБ(да асус не смогла всосать все доступные для и9 192ГБ), отобрать у себя возможность сделать DP систему ради 400 долл (а если брать железо в ЦОДе так и вообще эти деньги будут размазаны на фоне общей цены)? Я на такое не пойду, это мое ИМХО.

Владимир

Владимир

Коллега - профессионально, это про рекомендации проверенных решений, а не теоретические возможности новых интелов на очень ограниченном спектре материнок, с ограниченным спектром ОЗУ. Когда я получу готовые проверенные решения (а не надпись в руководстве асус о том что надо посмотреть проверенную память по списку асус, в котором найду 3 модели озу якобы работающие с определенными процами, а если не заведется - то ссзб, да еще противоречивые отзывы на формуах - у кого-то завелось, у кого-то нет), тогда я без проблем поддержку Вашу точку зрения. А пока я лучше поддержжу ну там кровавых HP-шников, которые не предлагают на новых корках 12/13ххх ЕСС память, а все равно вставляют зеоны. Буду работать по их схеме.

так работайте, не использовать послепандемийные поколения процов надёжнее, я просто прошу вас не обманывать и не передёргивать факты, а в том что вы тут написали не имею никаких противоречий

Autumn

Autumn

так работайте, не использовать послепандемийные поколения процов надёжнее, я просто прошу вас не обманывать и не передёргивать факты, а в том что вы тут написали не имею никаких противоречий

по существу выше я рассчет кинул, где и кого я обманываю?

Владимир

Владимир

по существу выше я рассчет кинул, где и кого я обманываю?

по существу ксеон этот полнейшее дно по сравнению с этим i9

Autumn

Autumn

с должным тестированием перед работой я бы рекомендовал именно второй вариант с i9

Вы это тестирование провели?

Владимир

Владимир

тесты публичны, если вам реально интересно что-то сравнить, можно списаться в выходные и я проведу для вас те тесты которые вы попросите)

Autumn

Autumn

ну или как минимум снизьте плз накал эмоций.

все норм, мне уже монопенисуально =) я оффтоп закрыл

Autumn

Autumn

тесты публичны, если вам реально интересно что-то сравнить, можно списаться в выходные и я проведу для вас те тесты которые вы попросите)

Вы мне коллега лучше тесты zfs on nvme сделайте как вот тут https://pastebin.com/ABt5zeWe мне достаточно raid10/raidz1/raidz2 на 4-х nvme =) можно только с recordsize 128 и 4K/32jobs =) очень хочется. Самому пока не на чем.

Владимир

Владимир

Вы мне коллега лучше тесты zfs on nvme сделайте как вот тут https://pastebin.com/ABt5zeWe мне достаточно raid10/raidz1/raidz2 на 4-х nvme =) можно только с recordsize 128 и 4K/32jobs =) очень хочется. Самому пока не на чем.

так закажите в хетснере такой сервак, как не на чем)), ну и я пересобирать пул не буду. Сделаю те тесты которые не потребуют пересборки. Всё таки на общественных началах), не хочу забыивать работой выходные)

Autumn

Autumn

так закажите в хетснере такой сервак, как не на чем)), ну и я пересобирать пул не буду. Сделаю те тесты которые не потребуют пересборки. Всё таки на общественных началах), не хочу забыивать работой выходные)

Выиграл я такой неделю назад на аукционе за 90 евро на 5 нвме, после этого хетцнер дважды прибил мою учетку без пояснения причин, причем оба раза после обращения в саппорт разбанил. Хорошо что я там из продакшина больше не держку =)

Владимир

Владимир

Autumn

Autumn

таких нет на аукционе

значит мое кто-то за меня подобрал - был Threadripper 2950X/128GB/5xU.2 960GB datacent nvme

Владимир

Владимир

Autumn

Autumn

я про i9 13900

забудьте, меня интересует сейчас лишь голая производительность nvme raid10 vs raidz и все это против sata ssd

Хач

Хач

Vladislav

Vladislav

Еще вопрос, кто гонял шифрование, какой оверхед дает? А связка сжатие+шифрование?

Где-то было тут что шифрование + сжатие странно работает

Vladislav

Vladislav

и на нативном шифровании со сжатием начинаются нюансы, и мета занимает больше

Не могу только найти какие

Autumn

Autumn

это была только что созданная учетка или старая?

обе, сначала блоканули старую, в которую я не заходил некоторое время, я написал в саппорт, они разблочили, мол я через впн заходил и сработала автоматика, потом они не просто заблочили ее, а заблочили с удалением всех продуктов (там все равно ничего не было поэтому пох), учетка была на двухфакторке + подтвержденная загранпаспортом, но я решил сделать другую - и как только я ее активировал, через пол часа пришло сообщение на почту, что она автоматически удалена со всеми сервисами, я пока забил болт писать в саппорт и бодаться с хетцнером, я давно с ними не работаю, поэтому позже уже займусь вопросом - я думал там купить самый дешевый сервак с 4 нвме для тестов на месяц, т.к. там самые низкие цены из всех ЦОДов с которыми я работаю на такое барахло

Autumn

Autumn

Где-то было тут что шифрование + сжатие странно работает

а если без сжатия, просто шифрование - тут стоит вопрос, надо в ЦОДе клиенту размещать конфиденциальные данные, так что бы даже там сняв винты нельзя было считать, поэтому рассматриваю вопрос включения шифрования

Vladislav

Vladislav

Autumn

Autumn

хотя без сжатия не прикольно, у меня на пулах в среднем 1.4-1.8х сжатие бывает, а иногда и 2х

Хач

Хач

обе, сначала блоканули старую, в которую я не заходил некоторое время, я написал в саппорт, они разблочили, мол я через впн заходил и сработала автоматика, потом они не просто заблочили ее, а заблочили с удалением всех продуктов (там все равно ничего не было поэтому пох), учетка была на двухфакторке + подтвержденная загранпаспортом, но я решил сделать другую - и как только я ее активировал, через пол часа пришло сообщение на почту, что она автоматически удалена со всеми сервисами, я пока забил болт писать в саппорт и бодаться с хетцнером, я давно с ними не работаю, поэтому позже уже займусь вопросом - я думал там купить самый дешевый сервак с 4 нвме для тестов на месяц, т.к. там самые низкие цены из всех ЦОДов с которыми я работаю на такое барахло

я тож новую создал и тут же заблочили. Мне кажется так они левых пассажиров фильтруют)) Через сапорт разблочили

Autumn

Autumn

так это со стороны гостевой ОС

в смысле? а если у меня просто сетевая хранилка, например 2 сервера, а один zfs и там smb/nfs сторадж прямо на нем висит

Autumn

Autumn

я тож новую создал и тут же заблочили. Мне кажется так они левых пассажиров фильтруют)) Через сапорт разблочили

ну типа да, они там реагируют, разблочивают, а потом опять автоматом блочат, пока нет времени бодаться с ними выясняя причины

Autumn

Autumn

А, такое даже

ну да, хочу файлопоймойку организовать и сливать на два сервера виртуализации цепляя по сети к виртуалкам как сетевой сторадж

Vladislav

Vladislav

ну да, хочу файлопоймойку организовать и сливать на два сервера виртуализации цепляя по сети к виртуалкам как сетевой сторадж

Хм, тогда нативное шифрование выход

Autumn

Autumn

Хм, тогда нативное шифрование выход

ну я о нем и думал, видел 45 drives активно юзают у себя на датасетах, но тут че-то как то некоторые не весело пишут https://www.reddit.com/r/zfs/comments/10dji4q/luks_on_a_zvol_is_it_possible_and_does_it_make/

Autumn

Autumn

Особенно вот это напрягает - I'm a bit worried about ZFS native encryption given the issues they had before where zfs send --raw would corrupt some metadata apparently.

Станислав

Станислав

@Wladimi @DanteAvalon @neurox в общем я понял, что человек с редита прав, был, пол года. Но потом выпустили чипсет W680, который действительно позволяет использовать UDIMM память с ECC. Подтверждение тому (для меня по крайней мере) есть список поддержки такой ОП у Asus

https://www.asus.com/ua-ua/motherboards-components/motherboards/workstation/pro-ws-w680-ace/helpdesk_qvl_memory/?model2Name=Pro-WS-W680-ACE

Vladislav

Vladislav

Владимир

Владимир

*Маршрутизация с кодом коррекции ошибок поддерживается в 4L*

можно ссылочку где эта приписка написана?

Станислав

Станислав

Еще вопрос, кто гонял шифрование, какой оверхед дает? А связка сжатие+шифрование?

Спросите у @underflow17 , он пробовал и нехорошо отзывался, на LUKS перешел.

А как вы решите вопрос конфиденциальности запуска при аварийных выключениях? Т.е. когда электричество рубанули, бывает такое, то нужно удаленно запустить машину, введя пароль. Только выключение не обязательно аварийное, вдруг это чей-то злой замысел и подмена initramfs?

Autumn

Autumn

Спросите у @underflow17 , он пробовал и нехорошо отзывался, на LUKS перешел.

А как вы решите вопрос конфиденциальности запуска при аварийных выключениях? Т.е. когда электричество рубанули, бывает такое, то нужно удаленно запустить машину, введя пароль. Только выключение не обязательно аварийное, вдруг это чей-то злой замысел и подмена initramfs?

Спс. Я еще не думал, поэтому спросил - у кого есть опыт реализации.

Алексей

Алексей

Спросите у @underflow17 , он пробовал и нехорошо отзывался, на LUKS перешел.

А как вы решите вопрос конфиденциальности запуска при аварийных выключениях? Т.е. когда электричество рубанули, бывает такое, то нужно удаленно запустить машину, введя пароль. Только выключение не обязательно аварийное, вдруг это чей-то злой замысел и подмена initramfs?

да, возможно я не раскурил полностью, но шифрование дает четырехкратное увеличение используемых иопсов

Станислав

Станислав

Спс. Я еще не думал, поэтому спросил - у кого есть опыт реализации.

Я на паре винртуалках так реализовал. Через dropbear подключаюсь по ssh, ввожу пароль. Но я забавы ради зашифровал, чтобы попробовать. А чтобы конфиденциально всё было, так как доступ прямой не имею, нужно ещё подумать

Владимир

Владимир

с сайта интел

на русском языке?, они же заблочили)

В общем я думаю такая формулировка намёк на то что в каких-то процах линейки нет поддержки ECC и она там не заявлена. В таком случае будет только базовое ECC доступное в DDR5

Ivan

Ivan

на русском языке?, они же заблочили)

В общем я думаю такая формулировка намёк на то что в каких-то процах линейки нет поддержки ECC и она там не заявлена. В таком случае будет только базовое ECC доступное в DDR5

https://www.google.com/search?client=firefox-b-e&q=+Доступно+на+отдельных+моделях+процессоров+в+сочетании+с+W680+PCH.+Маршрутизация+с+кодом+коррекции+ошибок+поддерживается+в+4L+для+всех+конфигураций+DDR4+и+DDR5.

Vladislav

Vladislav

Autumn

Autumn

Эрм, нет, это первая часть

А вторая именно некий L4

Похоже на маркетинговый булшит, типа увидели сноску, пошли посмотреть о чем речь, а там все шоколадно - мол для какого-то там L4 роутинга ЕСС включен и на ДДР4 и на ДДР5. По сути я думаю тут речь идет об интеловской платформе RAS - reliability, availability, serviceability, там в разделе reliability, касательно DDR есть указание на аппаратный DDR parity check почти в реальном времени, по сути как я понимаю обычные для всех DDR(да оно и в DDR3 было, а вот на DDR2 опционально) parity-check для командно-адресной шины. Т.е. для команд и адресов считается контрольная сумма и шлется в регистры DIMM, там для них пересчитывается контрольная сумма и сверяется с той что пришла. Если случилась беда, то контроллер памяти об этом информируется, а транзакция отменяется. По моему так это работает и это стандартная функция в современном железе, ничего такого интел не изобрел. Короче ни о чем, я остаюсь при факте что некоторые десктопные процы на 680-м чипсете могут работать с ЕСС, но надо найти недорогую связку проца+мать, ну и дождаться когда в ядро линупса завезут нормальный планировщик для сраных Р/Е ядер, а так выходит купишь i9-13700К, а на выходе имеет 8 ядер 16 потоков и ТДП в 250Вт(или сколько там для раскочегареных 6Ггц).

Владимир

Владимир

Autumn

Autumn

Так планировщик уже распределяет на оба типа ядра, другой вопрос на сколько это уместно сейчас работает

Не совсем уместно с контейнерами, я кидал чат kvm/pve видос теста на i5 прокса - виртуалки норм, а с контейнерами беда, т.е. можно выделить контейнеру 4 ядера и из них получить два Р и два Е , ну вобщем гляньте, видео свежее 2 мес. на свежем проксе. Так что еще есть проблемы, хотя платформе уже сколько лет + интел донатит в линукс, так че не напишет код что бы его поделия работали как надо?

Владимир

Владимир

Владимир

Владимир

Не совсем уместно с контейнерами, я кидал чат kvm/pve видос теста на i5 прокса - виртуалки норм, а с контейнерами беда, т.е. можно выделить контейнеру 4 ядера и из них получить два Р и два Е , ну вобщем гляньте, видео свежее 2 мес. на свежем проксе. Так что еще есть проблемы, хотя платформе уже сколько лет + интел донатит в линукс, так че не напишет код что бы его поделия работали как надо?

Пока для меня эта проблема не критична, поэтому никак не копал в этом направлении, либо это пофиксят когда для меня станет критично, либо прийдётся самому разбираться)

Autumn

Autumn

Пока для меня эта проблема не критична, поэтому никак не копал в этом направлении, либо это пофиксят когда для меня станет критично, либо прийдётся самому разбираться)

Для меня не критично если я собираю хранилки на зфс и не более, т.е. тут мне по барабану что у того же i9-13700 будут пахать только 8 Р ядер, но встает другой вопрос - а оно мне за такую цену надо? Для хранилки можно взять гораздо дешевле зеон+есс память. Если же я собираю гиперконвергент типа прокскластер+зфс+репликация, то мне такие мансы не нужны, я буду искать классическую схему где будет гарантированно предсказуемое распределение ресурсов.

Владимир

Владимир

Для меня не критично если я собираю хранилки на зфс и не более, т.е. тут мне по барабану что у того же i9-13700 будут пахать только 8 Р ядер, но встает другой вопрос - а оно мне за такую цену надо? Для хранилки можно взять гораздо дешевле зеон+есс память. Если же я собираю гиперконвергент типа прокскластер+зфс+репликация, то мне такие мансы не нужны, я буду искать классическую схему где будет гарантированно предсказуемое распределение ресурсов.

Тут зависит от задач, так что да, не всем это подходит

Artem

Artem

Для меня не критично если я собираю хранилки на зфс и не более, т.е. тут мне по барабану что у того же i9-13700 будут пахать только 8 Р ядер, но встает другой вопрос - а оно мне за такую цену надо? Для хранилки можно взять гораздо дешевле зеон+есс память. Если же я собираю гиперконвергент типа прокскластер+зфс+репликация, то мне такие мансы не нужны, я буду искать классическую схему где будет гарантированно предсказуемое распределение ресурсов.

А ничо, что для Р-ядер нужно отрубать гипертрединг, чтобы что-то в плане перформанса гарантировать?

Владимир

Владимир

А ничо, что для Р-ядер нужно отрубать гипертрединг, чтобы что-то в плане перформанса гарантировать?

не вижу смысла, если речь про виртуализацию конечно и большой многопоток на сервере. Если многопотока большого нет, то может ты и прав

Artem

Artem

Мне вспомнилось где-то вычитанное (но пруфов не найду), что Р-ядро > Е-ядро > Р-потока в режиме НТ. И если это правда, то тут начинается куча совсем неудобных вопросов...

Autumn

Autumn

А ничо, что для Р-ядер нужно отрубать гипертрединг, чтобы что-то в плане перформанса гарантировать?

А ниче, что претензия не по адресу, Вам коллега сюда - support@intel.com =)

Artem

Artem

А ниче, что претензия не по адресу, Вам коллега сюда - support@intel.com =)

Схему-то ты ищешь исходя из возможностей. Так чо - НТ отрубаешь? ;)

Autumn

Autumn

Мне вспомнилось где-то вычитанное (но пруфов не найду), что Р-ядро > Е-ядро > Р-потока в режиме НТ. И если это правда, то тут начинается куча совсем неудобных вопросов...

https://www.youtube.com/watch?v=BwNrKU2LA3M вот тут это как раз и показано, для ВМ сначала задействуются Р, затем Е и лишь потом гипер. Правда с контейнерамы не выходит ... все через одно место.

Autumn

Autumn

Схему-то ты ищешь исходя из возможностей. Так чо - НТ отрубаешь? ;)

Схему для чего? Причем тут я и НТ? Исчезни.

Artem

Artem

Fedor

Fedor