Влада

Влада

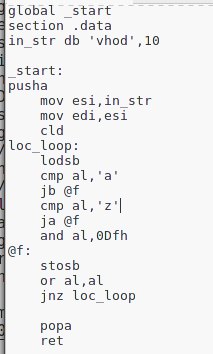

Добрый день! Стоит задача перевести исходную строку в верхний регистр. Ассемблер очень плохо знаю. Код нашла на просторах интернета. Подскажите, пожалуйста, в чем причина неверной работы?

Eugene

Eugene

Добрый день! Стоит задача перевести исходную строку в верхний регистр. Ассемблер очень плохо знаю. Код нашла на просторах интернета. Подскажите, пожалуйста, в чем причина неверной работы?

В том, что строка оканчивается 10, а не 0, когда код отрабатывает до символа 0.

А вообще, странно, что функция перевода строки в верхний регистр называется _start :)

Или это вся программа? Какая ОС (Windows, Linux, DOS (DOSBox))?

Влада

Влада

Eugene

Eugene

да

Через ret не выходят.

Выходят через

mov eax,1

xor ebx,ebx

int 80h

Это если без вывода результата на экран.

Eugene

Eugene

mov eax, 4

mov ebx, 1

mov ecx, in_str

mov edx, 5

int 80h c выводом результата

Всё правильно. И выход тоже предыдущее тоже (это эквивалентно тому, что я написал).

Только ret надо убрать тогда.

А после 10 добавить 0 ('vhod',10,0).

електр🟢нік ✙🟠рчбеч ඞ

електр🟢нік ✙🟠рчбеч ඞ

електр🟢нік ✙🟠рчбеч ඞ

електр🟢нік ✙🟠рчбеч ඞ

Хотя, х/з, может, и ret сработает, я не вот прям линуксоид...

там crt стдлибовский подтягивается обычно

Eugene

Eugene

там crt стдлибовский подтягивается обычно

С чего бы это вдруг?

Смотря как и чем компилировать.

Если просто:

nasm -f elf test.asm -o test.o

ld -s test.o -o test

...то никакого crt не будет.

Да и без main как crt будет работать?

Eugene

Eugene

Кто-нибудь знает, чему равны загадочные значения MAX_HLE_NEST_COUNT и MAX_RTM_NEST_COUNT (уровни вложенности для TSX) или как их узнать программно?

В Intel-A SDM вообще об их значениях ничего не сказано, даже MSR таких нет.

Aiwan \ (•◡•) / _bot

Aiwan \ (•◡•) / _bot

Eugene

Eugene

вот я и спрашиваю, мож опечатался tsx/tss

Нет, не опечатался. Да и я ж конкретно про константы спрашиваю. Там даже в них есть ключевые слова: HLE, RTM :)

JeisonWi

JeisonWi

Посмотри в утекших исходниках UEFI могут быть

Всмысле в «утёкших»? TianoCore есть на гитхабе.

А помимо Тианы есть ещë реализации UEFI, интересно?

ТианоКор это полноценная свободная реализация, без блобов. А так есть куча «форков», например, apple использовали свою версию, когда оно было ещё первой ревизии.

Есть Clover, загрузчик Mac OS X на «обычном» железе, имеющий в своём составе модифицированный тиано.

JeisonWi

JeisonWi

Всмысле в «утёкших»? TianoCore есть на гитхабе.

Это лишь малая часть. Вендоры имеют свои модификации, плюс там кода работающего с самим железом нет, так называемый PI - Platform Initialization

JeisonWi

JeisonWi

Туда же входит и Intel MRC - Memory Reference Code, там часто можно найти MSR, которых нет в доках

Eugene

Eugene

Посмотри в утекших исходниках UEFI могут быть

А какое отношение UEFI может иметь к TSX? Вы точно о том говорите? Это Translational Synchronization Extensions, аппаратная реализация транзакционной памяти для многопоточных программ. Реализуется расширениями HLE (префиксы xacquire, xrelease) и RTM (инструкции xbegin, xend, xabort, xtest).

Константы, о которых я спрашиваю — это аппаратные, опять же, ограничения глубины вложенности. Причём тут UEFI ? 🤷♂

Eugene

Eugene

Вчера тестил HLE дома через SDE (ибо у меня такой фичи нет).

Забавно так: меняешь значение мьютекса из потока (скажем, с 0 на 1 через xacquire lock inc [m]), читаешь это значение, там 1. Читаешь из другого потока, он видит его как 0. Т.е. оно меняется только для того потока, который его изменил. Если во втором потоке записать туда 2 (так же через xacquire), третий поток всё равно увидит 0 (а первый 1, второй 2).

Мне вот интересно, как это решается для потоков, которые выполняются на одном ядре (без учёта HT даже)? Участвует ли в этом каким-либо образом ОС?

И остаются ли мьютексы всегда в кэше (ведь физически они вряд ли записываются в память)? Короче, надо нормально по-RTFM-ить.

Eugene

Eugene

Вызов WinAPI внутри блока приводит к аборту из-за «unfriendly instruction» jmp far. Видимо, при переходе в ядро. Короче, надо хорошенько такие вещи профилировать, дабы они не работали неожиданными образом.

JeisonWi

JeisonWi

А какое отношение UEFI может иметь к TSX? Вы точно о том говорите? Это Translational Synchronization Extensions, аппаратная реализация транзакционной памяти для многопоточных программ. Реализуется расширениями HLE (префиксы xacquire, xrelease) и RTM (инструкции xbegin, xend, xabort, xtest).

Константы, о которых я спрашиваю — это аппаратные, опять же, ограничения глубины вложенности. Причём тут UEFI ? 🤷♂

Это при том, что это инициализируется каким либо образом при старте железа

Eugene

Eugene

Хм, я думал, что в железе это вообще как-то зашито жёстко. Хотя, откуда память под это всё выделяется — хз. Странно, что доки молчат об этих числах.

Eugene

Eugene

Влючение поддержки AVX в real-mode:

org 0x100

; Enable SSE

mov eax,cr0

and al,0xFB ; clear coprocessor emulation CR0.EM (bit 2)

or al,0x2 ; set coprocessor monitoring CR0.MP (bit 1)

mov cr0,eax

mov eax,cr4

or eax,0x40600 ; set CR4.OSFXSR (bit 9), CR4.OSXMMEXCPT (bit 10) and CR4.OSXSAVE (bit 18)

mov cr4,eax

; Enable AVX

xor ecx,ecx

xgetbv ; load XCR0 register

or al,7 ; set AVX, SSE, x87 bits

xsetbv ; save back to XCR0

; Test SSE

xorps xmm0,xmm0

xorps xmm1,xmm1

addss xmm0,xmm1

; Test AVX

vzeroupper

vxorps xmm0,xmm0,xmm0

vxorps xmm1,xmm1,xmm1

vaddps xmm2,xmm0,xmm1

ret

Запускаю в VMware (MS-DOS).

Доходит до vzeroupper и виснет.

Что ему ещё не хватает?

Eugene

Eugene

Даже добавляю код из Intel SDM для проверки поддержки AVX, выдаёт, что всё ок.

mov eax, 1

cpuid

and ecx, 018000000H

cmp ecx, 018000000H; check both OSXSAVE and AVX feature flags

jne not_supported

; processor supports AVX instructions and XGETBV is enabled by OS

mov ecx, 0; specify 0 for XCR0 register

xgetbv ; result in EDX:EAX

and eax, 06H

cmp eax, 06H; check OS has enabled both XMM and YMM state support

jne not_supported

mov eax, 1

jmp done

not_supported:

mov eax, 0

done:

електр🟢нік ✙🟠рчбеч ඞ

електр🟢нік ✙🟠рчбеч ඞ

А почему не должно?

потому что префиксы c4 и c5 это vex и evex они в реалмоде вроде как заняты опкодами les и lds

електр🟢нік ✙🟠рчбеч ඞ

електр🟢нік ✙🟠рчбеч ඞ

https://software.intel.com/en-us/forums/intel-isa-extensions/topic/297055 это не читал но из названия понятно

електр🟢нік ✙🟠рчбеч ඞ

електр🟢нік ✙🟠рчбеч ඞ

>>Oh, right, I forgot that VEX prefix only works in 16-bit protected mode, not in real mode or V86.

Eugene

Eugene

https://software.intel.com/en-us/forums/intel-isa-extensions/topic/297055 это не читал но из названия понятно

Ох, спасибо! Попробую в PMode перейти и там проверить.

Eugene

Eugene

потому что префиксы c4 и c5 это vex и evex они в реалмоде вроде как заняты опкодами les и lds

Дизассемблер, к примеру, HIEW однозначно декодирует AVX именно как AVX, а не как LDS, LES и пр.

В PMode (не x64) тоже есть LDS и LES.

Eugene

Eugene

Всё верно.

Заменил or al,0x2 на or al,0x3 и добавил в конец:

mov eax,cr0

and al,not 1

mov cr0,eax

И всё заработало.

Leon

Leon

Всё верно.

Заменил or al,0x2 на or al,0x3 и добавил в конец:

mov eax,cr0

and al,not 1

mov cr0,eax

И всё заработало.

Т.е. ты на милисекундочку перешел в пм а потом обратно?

Eugene

Eugene

Т.е. ты на милисекундочку перешел в пм а потом обратно?

Да. Если не менять сегментные регистры, можно даже с памятью работать так же, как в RM :)

Про cli/sti — это конечно. Уж не стал сообщение редактировать.

А по поводу МИЛЛИсекундочки... Я тут померил скорость переключения RM-PM-RM (т.е. туда и обратно в цикле), у меня под ВМтраврь получилось полмиллиона пар переключений в секунду. Т.е. довольно неплохая скорость. Так что, при жгучем нежелании работать всё время под PM, можно даже приключаться, когда надо, туда-сюда :). Не вот прям красота, но если очень нннадо, то можно.

Eugene

Eugene

Для чистоты эксперимента (замера скорости) можно разбавить переключения ещё каким-то кодом. И замерить ещё в чистом DOS'е и на AMD, ибо дело было на Intel.

Aiwan \ (•◡•) / _bot

Aiwan \ (•◡•) / _bot

Это чо сессия что ли

они хоть не пишут, а у меня уже 3е с однотипными заданиями

Eugene

Eugene

В соседнем чате (@pro_osdev) возник вопрос о том, уместно ли здесь (в @proasm) говорить про разработку драйверов.

Хорошо бы зафиксировать где-то в описании, является ли данный чат обсуждением низкоуровневых вещей, а не только асма.

@AlexFails одобрил эту идею. Дело за малым — это как-то обозначить.

По сути, просто в описание можно добавить строку типа "Чат об ассемблере, реверсе и низкоуровневом программировании в целом."

Давайте сделаем, у кого есть права на это.

Eugene

Eugene

привет;

идея хорошая, тип low-level.

Формально, я считаю, что это допустимо в рамках чатика (как и прочий реверс, непопсовые железки, етц);

Надо будет, наверное, уточнить описание чата

Vladimir

Vladimir

bilka00

bilka00

Yura

Yura

Co(n)stantine👨🔬

Co(n)stantine👨🔬