Ilyxa

Ilyxa

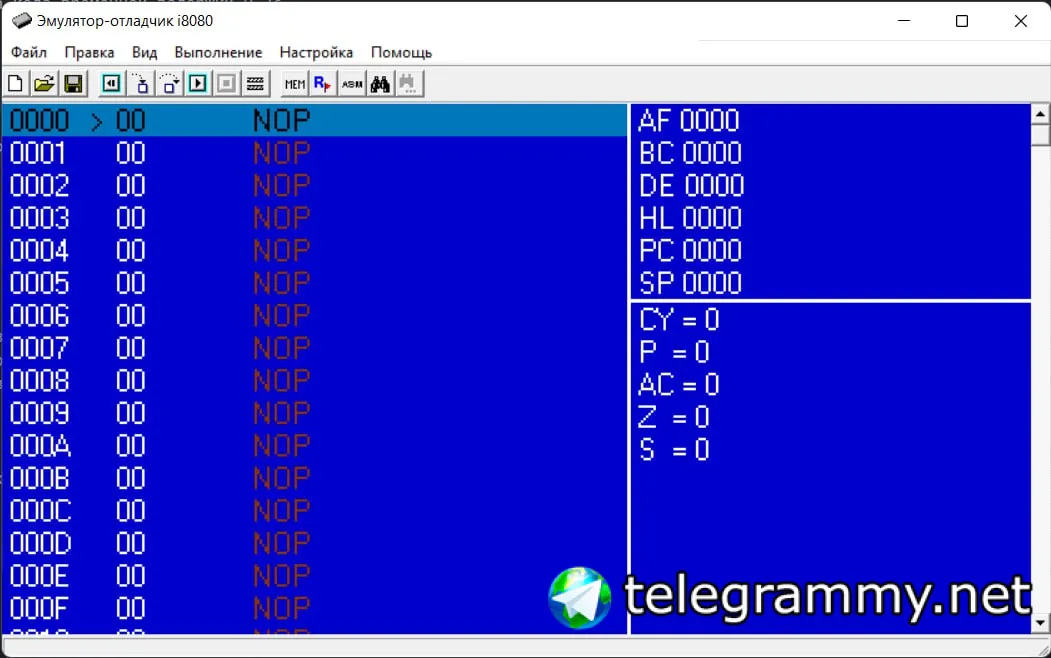

Ребят привет, как мне сделать счетчик в цикле, мне не хватает регистров для этого, мне нужно чтобы cycle2 выполнился 4 раза, поэтому делаю так MVI C, 4 , но когда доходит код до строчки LXI B, 0x2D92, в С записывается 92, поэтому цикл ломается, так как B это регистровая пара BC, как можно решить это дело?

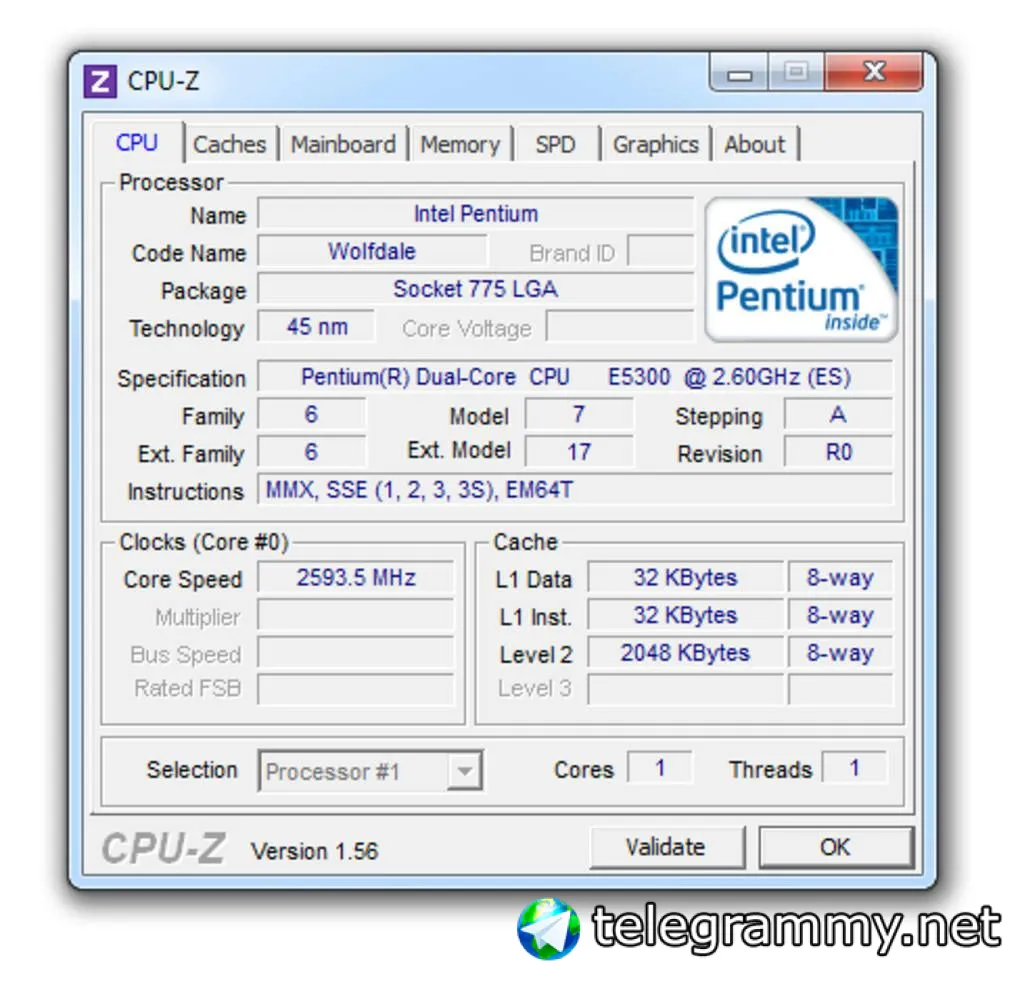

Ассемблер род процессор i8080

START:

LXI H, 0x02B3 ; начальная установка указателей

LXI D, 0x02B3 ; начальная установка указателей

CYCLE:

MOV A, M ; загрузка кода символа по указателю 1

STA 0x83F8 ; Адрес первого индикатора

MVI C, 4 ; Кол-во выполения цикла

CYCLE2:

MOV A, M ; загрузка кода символа по указателю 1

STA 0x83F8 ; Адрес первого индикатора

LDAX D ; Загружаем в A значение из DE

STA 0x83F9 ; Адрес второго индикатора

INX D

LXI B, 0x2D92 ;загрузка кода временной задержки 0.7c

CALL TIMER

CALL TIMER

DCR C ; Декрементируем счетчик цикла

JNZ CYCLE2 ; Если не ноль, крутим цикл еще раз

; Меняем HL на 4 цифры вперед из-за последовательность

INX H

INX H

INX H

INX H

MOV A, L ; Записываем в A регистр L

CPI C3H ; Сравнивем его с последней цифрой таблицы, отдает ноль если равно

JNZ CYCLE ; Если не равно 0, прыгаем дальше

JMP START ; Если равно нулю, то прыгаем на начало последовательности

TIMER:

DCX B ; число машинных тактов равно 5

MOV A, B ; 5

ORA C ; 4

JNZ TIMER ; 10

RET

The Bird of Hermes

The Bird of Hermes

Ilyxa

Ilyxa

В стек кидать пробовал?

Нет, мне говорят, не может быть такого, что не хватает регистров для этого дела

The Bird of Hermes

The Bird of Hermes

Нет, мне говорят, не может быть такого, что не хватает регистров для этого дела

...

Push B

Lxi b, 0x2d92

Call timer

Call timer

Pop B

...

Попробуй так

Ilyxa

Ilyxa

...

Push B

Lxi b, 0x2d92

Call timer

Call timer

Pop B

...

Попробуй так

А не С надо грузить в стек?

The Bird of Hermes

The Bird of Hermes

Мне больше интересно, где ты ассемблер используешь?)

Ну в основном для себя, недавно только подвернулось что-то, где можно его использовать... Может быть

Ilyxa

Ilyxa

Но у i8080 совсем по-другому, это серьёзно отличается от 86 и старше

Ilyxa

Ilyxa

Под какую ось?

Под винду, по сути тоже как учебка, стандартные команды

Что-то существенное, реальных задач не было

The Bird of Hermes

The Bird of Hermes

Под винду, по сути тоже как учебка, стандартные команды

Что-то существенное, реальных задач не было

Не то чтобы на асме особо пишут какие-то большие задачи. Я винду сам ковырял в плане Асма, но там всё веселье портят системные вызовы

The Bird of Hermes

The Bird of Hermes

А ты где работаешь, если не скрываешь и чем занимаешься?

Учусь ещё, работаю педагогом дополнительного образования

The Bird of Hermes

The Bird of Hermes

Крутяк

А сам в какую сферу хочешь?

Некоторое время позаниматься педагогикой, потом заняться разработкой чего-нибудь

Ilyxa

Ilyxa

Асм конечно бустит в плане программирования, у нас еще Си был на первом курсе, там это для меня был разрыв шаблона

The Bird of Hermes

The Bird of Hermes

То есть не хочешь в ассемблер уходить?

Ну в плане не хочу, мне ассемблер на самом деле нравится, но я не вижу большого количества направлений для чистого ассемблера. Полноценная разработка на нём требует слишком много времени, что непозволительно для больших проектов. Можно использовать разве что как дополнения, этакие вставки

Ilyxa

Ilyxa

...

Push B

Lxi b, 0x2d92

Call timer

Call timer

Pop B

...

Попробуй так

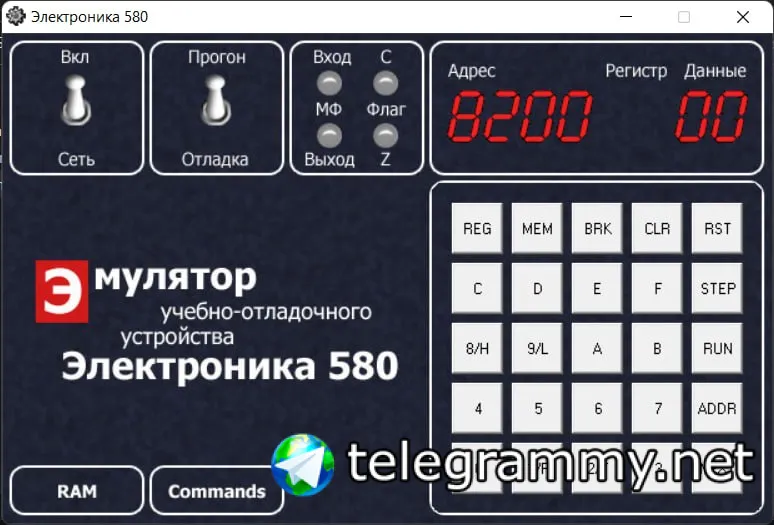

Спасибо, в эмуляторе прокатило, осталось прогнать на рабочей старушке

The Bird of Hermes

The Bird of Hermes

Асм конечно бустит в плане программирования, у нас еще Си был на первом курсе, там это для меня был разрыв шаблона

Ассемблер позволяет понять, что такое язык программирования, принцип работы компиляторов, как хранятся данные в памяти, лучше понять абстракцию, указатели.

Ilyxa

Ilyxa

Ну в плане не хочу, мне ассемблер на самом деле нравится, но я не вижу большого количества направлений для чистого ассемблера. Полноценная разработка на нём требует слишком много времени, что непозволительно для больших проектов. Можно использовать разве что как дополнения, этакие вставки

Имеешь в виду вставки в код, допустим в c++?

Для ускорения каких-то фрагментов?

The Bird of Hermes

The Bird of Hermes

Имеешь в виду вставки в код, допустим в c++?

Для ускорения каких-то фрагментов?

Да, я думаю оптимально именно так

The Bird of Hermes

The Bird of Hermes

Просто слышал, что все пытаются уйти от ассемблера, мол дорого

Скорее долго. Что для обучения, что для написания

Ilyxa

Ilyxa

Ассемблер позволяет понять, что такое язык программирования, принцип работы компиляторов, как хранятся данные в памяти, лучше понять абстракцию, указатели.

А если еще в купе изучать устройство МП, как там бегают нулики и единички, то вообще здорово

The Bird of Hermes

The Bird of Hermes

А если еще в купе изучать устройство МП, как там бегают нулики и единички, то вообще здорово

Да, это неплохо, мне с этим правда не повезло, так что я с этим знаком почти никак

Eugene

Eugene

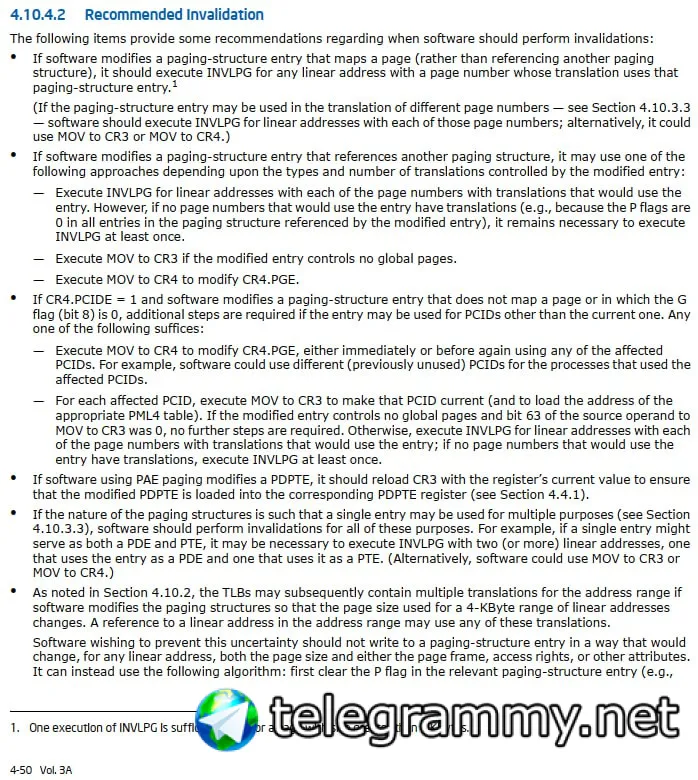

Господа асмописатели, как думаете, что дороже и насколько, одиночный invlpg, или промах по TLB?

PS: архитектура x86-64, уточнения для разных процессоров тоже приветствуются

Однозначно не скажешь, но судя по сайту uops.info инструкция invlpg требует от сотни до 2+ сотен тактов. Промах TLB - 10-100 тактов (https://en.m.wikipedia.org/wiki/Translation_lookaside_buffer)

Eugene

Eugene

Но по логике, если при TLB miss нужная запись таблицы страниц отсутствует в кэшах, то на её загрузку могут потребоваться сотни тактов (200-400, например — числа взяты из одной видеолекции по оптимизации).

disba1ancer

disba1ancer

Но по логике, если при TLB miss нужная запись таблицы страниц отсутствует в кэшах, то на её загрузку могут потребоваться сотни тактов (200-400, например — числа взяты из одной видеолекции по оптимизации).

Invlpg полностью стирает все кеши самих таблиц страниц

Eugene

Eugene

Invlpg полностью стирает все кеши самих таблиц страниц

Я про кэши L1-L3.

Вообще, интересен контекст, почему такое странное сравнение?

disba1ancer

disba1ancer

Я про кэши L1-L3.

Вообще, интересен контекст, почему такое странное сравнение?

Про обычные кэши речь не идёт

disba1ancer

disba1ancer

Я про кэши L1-L3.

Вообще, интересен контекст, почему такое странное сравнение?

Нужно понять когда выгоднее инвалидировать всю TLB, вместо инвалидации большого числа записей

Eugene

Eugene

А при чем тут скорость промаха? Ты хочешь инвалидировать её путём вытеснения остальных записей?

disba1ancer

disba1ancer

А при чем тут скорость промаха? Ты хочешь инвалидировать её путём вытеснения остальных записей?

Потому что в результате полной инвалидации потребуется заполнить TLB с нуля, но очистка делается 1-2мя инструкциями, в то время как неполная очистка потребует вызова инвалидации на каждую изменённую запись, поскольку мы не знаем какие из записей есть в TLB и есть ли вообще, потому получается, что мы либо теряем перф на инвалидации страница за страницей, либо гарантированно получая много промахов потом, хотелось бы завести динамическую стратегию, которая при большом количестве изменяемых записей страниц просто инвалидирует всё поскольку это в перспективе дешевле постраничной инвалидации

Eugene

Eugene

Потому что в результате полной инвалидации потребуется заполнить TLB с нуля, но очистка делается 1-2мя инструкциями, в то время как неполная очистка потребует вызова инвалидации на каждую изменённую запись, поскольку мы не знаем какие из записей есть в TLB и есть ли вообще, потому получается, что мы либо теряем перф на инвалидации страница за страницей, либо гарантированно получая много промахов потом, хотелось бы завести динамическую стратегию, которая при большом количестве изменяемых записей страниц просто инвалидирует всё поскольку это в перспективе дешевле постраничной инвалидации

Я так и не понял, какова цель. Зачем тебе эта инвалидация? Ты меняешь больше кол-во записей в таблице страниц. Иии?

disba1ancer

disba1ancer

Я так и не понял, какова цель. Зачем тебе эта инвалидация? Ты меняешь больше кол-во записей в таблице страниц. Иии?

Из двух стратегий выбрать ту которая в конкретной ситуации будет эффективнее

Eugene

Eugene

Из двух стратегий выбрать ту которая в конкретной ситуации будет эффективнее

Эффективнее для чего? Какова конечная цель?

disba1ancer

disba1ancer

Эффективнее для чего? Какова конечная цель?

для изменения произвольно заданного набора страниц

Eugene

Eugene

для изменения произвольно заданного набора страниц

Eugene

Eugene

Можно ещё исходить от логики. Если ты меняешь страницы, чтобы загрузить их в своп, то логично, что в TLB их нет (и при выгрузке тоже вряд ли, да и они там нафиг не нужны). Если при создании процесса, то ты при переключении контекста всё равно будешь CR3 менять. И т.д.

disba1ancer

disba1ancer

disba1ancer

disba1ancer

Можно ещё исходить от логики. Если ты меняешь страницы, чтобы загрузить их в своп, то логично, что в TLB их нет (и при выгрузке тоже вряд ли, да и они там нафиг не нужны). Если при создании процесса, то ты при переключении контекста всё равно будешь CR3 менять. И т.д.

cr3 можно менять так, чтобы ничего не инвалидировать

Leon

Leon

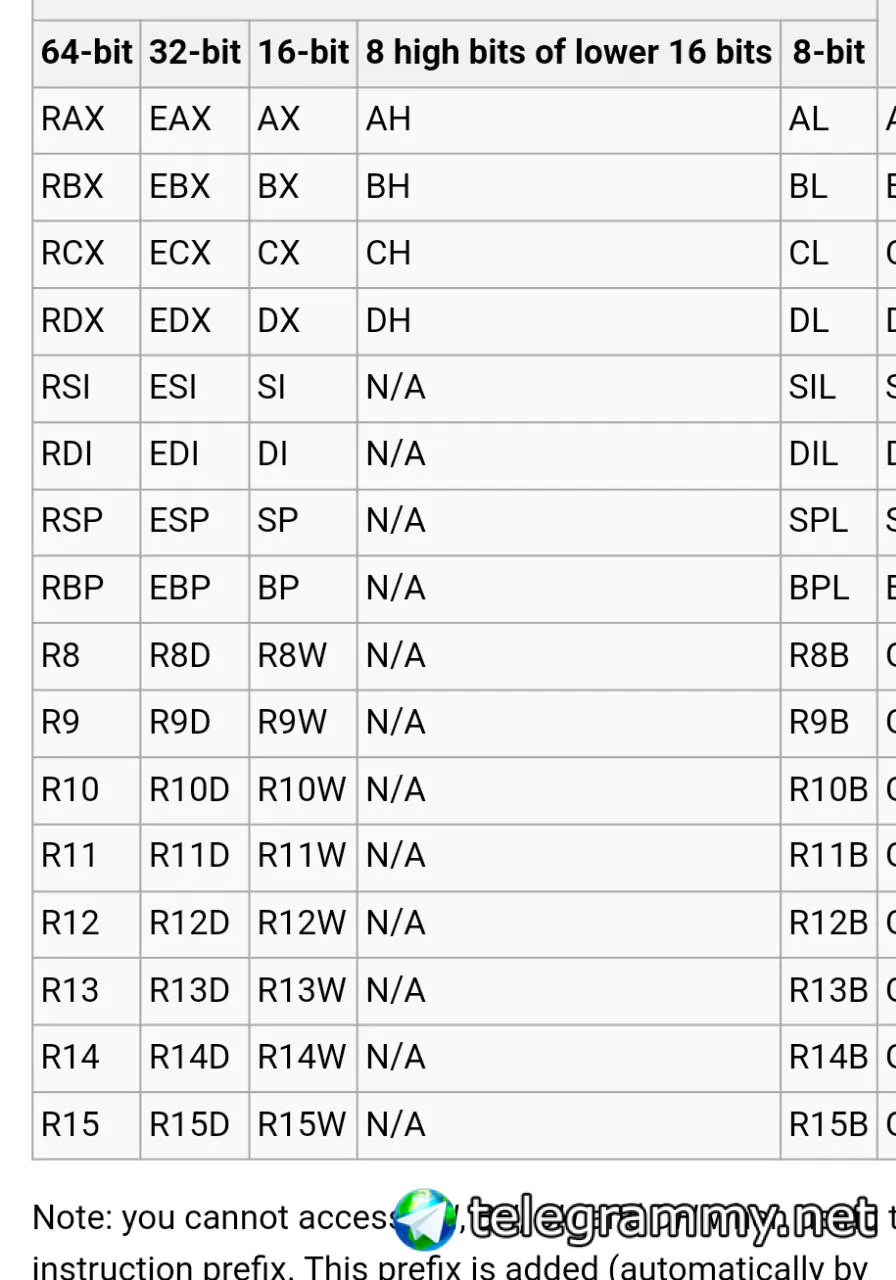

Можно как-то обращаться к младшим частям регистров r8-r15 в x64?

https://wiki.osdev.org/CPU_Registers_x86-64

disba1ancer

disba1ancer

Каждый такой регистр, это пачка из нескольких значений, то как процессор будет их интерпретировать зависит от используемой инструкции, каждый регистр имеет размер 128 бит в котором может поместится 4 32ух битных флота или 2 64ёх битных дабла, в более новых версиях SSE добавили целочисленные инструкции, которые по принципу работы похожи на MMX

Aiwan \ (•◡•) / _bot

Aiwan \ (•◡•) / _bot

не паралельное вычислление, а работа с "пачкой" данных идет в 1й инструкции. все это следует из самого названия - SIMD

Eugene

Eugene

В 32х битах по 8 xmm, ymm регистров, в 64х битах - по 16. zmm-регистров 32 в 64х битах, в 32х битах не помню.

Инфу брать в манах Intel:

xk8.ru/inteldoc

Тами описание отдельных инструкций и куча всякой инфы.

А вообще, если поискать на озоне книги со словами "Ассемблер avx", найдётся 2 книги про SIMD (тут они тоже есть: xk8.ru/asmlinks)

Eugene

Eugene

Ну вот как раз потом можно и Куссвюрма почитать :)

Прежде чем копать вглубь, сначала пойми всё на более высоком уровне абстракции.

Eugene

Eugene

ᅠ

ᅠ

Zyrocat

Zyrocat

Ask

Ask