Aiwan \ (•◡•) / _bot

Aiwan \ (•◡•) / _bot

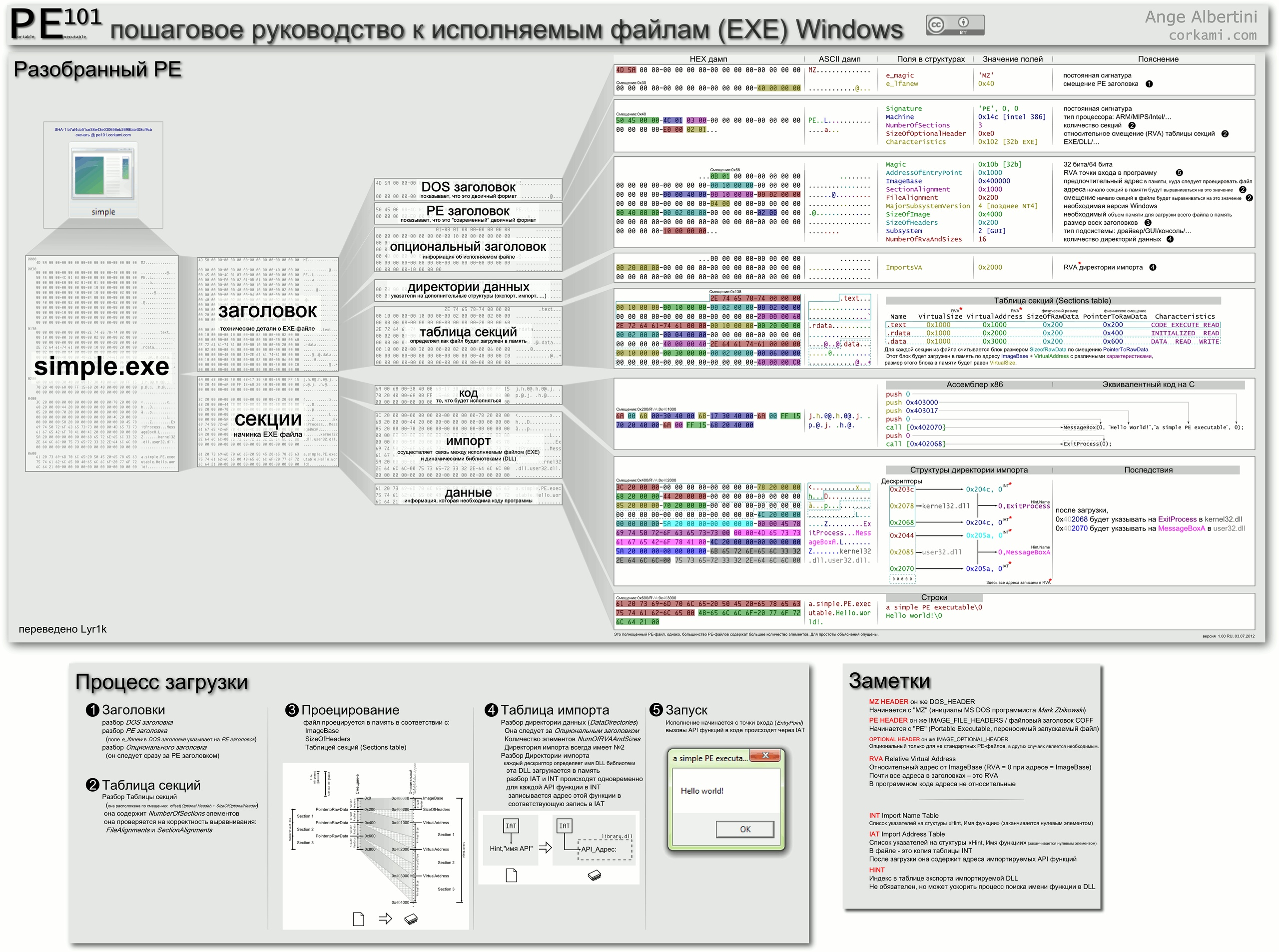

https://vk.com/@codeby_net-0x01-issleduem-portable-executable-exe-fail-format-pe-faila

🦋

🦋

В каких случаях используются инструкции например andn / orn, т.е. которые сначала выполняют логическую операцию, а потом делают NEG над вторым аргументом?

Eugene

Eugene

Не neg, а not, наверное?

Надо смотреть для конкретного процессора/контроллера, могут отличаться.

Для Intel:

and a,b — выделяет в a установленные биты по маске b

andn z,a,b — выделяет в a сброшенные биты по маске b, переводя их в 1, и записывает в z (условно and z,0101b,0011b запишет 0010b)

Eugene

Eugene

Бывает, что нужно не единицы выделить, а нули (или определить сразу все единицы). К примеру.

Классика:

and eax,edx

jz @fuck ; ни один бит edx в eax не установлен

И вот так:

andn ecx,eax,edx

jz @good ; все биты edx в eax установлены

Eugene

Eugene

Если как ты описываешь, тогда х/з. Может, не над вторым аргументом, а над результатом?

И сколько там всего операндов?

🦋

🦋

Если как ты описываешь, тогда х/з. Может, не над вторым аргументом, а над результатом?

И сколько там всего операндов?

https://www.felixcloutier.com/x86/andn

Eugene

Eugene

Ну, так это интеловский andn. Сначала not второго операнда, а потом and. Пример использования выше.

Ned

Ned

кстати, тут ведь не только про x86-й ассемблер, верно? мне вот интересно (не к спеху), как устроены прерывания в ARM. Коллеги сказали, там чуть ли не 16 уровней приоритетов... Чёт меня с этого удивило слегка.

Eugene

Eugene

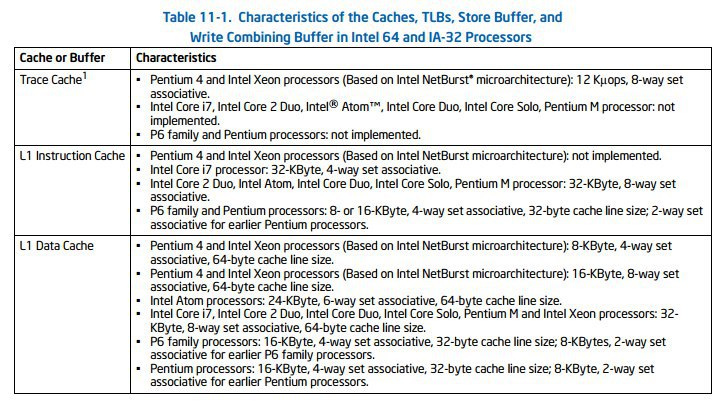

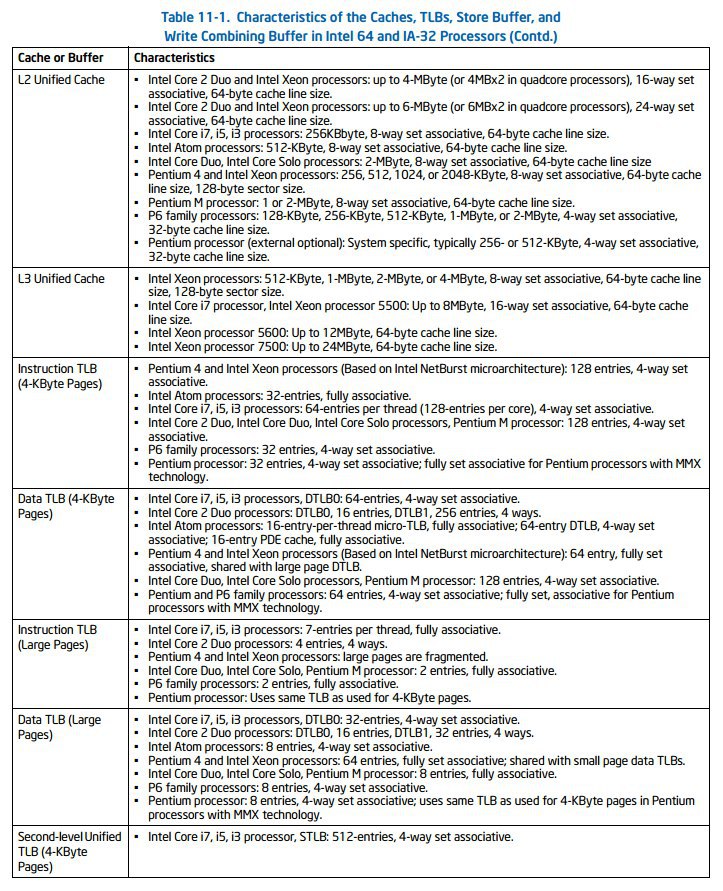

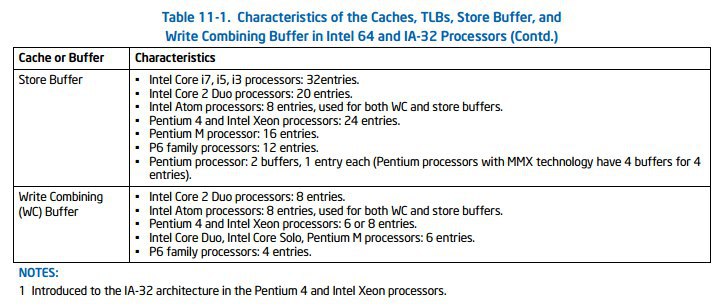

Размер линии кэша в х86 всегда 64 байта?

Вроде в мане написано, что по крайней мере, 32. Но обычно 64. Всегда или нет, не скажу. Мне кажется, что через cpuid можно определить.

Eugene

Eugene

👍

mov eax,1

cpuid

shr ebx,5

and ebx,255*8

; EBX = cache line size for CLFLUSH (bits 8..15 * 8)

Написано, что clflush флашит линию кэша, значит так можно получить размер. У меня показывает 64 байта.

Eugene

Eugene

Вот ещё:

mov eax,80000006h

cpuid

and ecx,255

; ECX = cache line size

Более надёжный, но тут надо сначала проверить - поддеживает ли cpuid конкретного процессора функцию 80000006h.

У меня тоже показывает 64 (i5, 2nd gen).

Eugene

Eugene

Вот, сделал универсальный вариант (сохраню себе тоже) 🙂

proc GetCacheLineSize

push ebx

mov eax,80000000h

cpuid ; get max ext. leaf level (EAX)

mov ecx,80000006h

cmp eax,ecx

jb @F

mov eax,ecx

cpuid ; cache size = ECX [0..7]

movzx eax,cl

jmp .ok

@@:

mov eax,1

cpuid ; cache size for CLFLUSH = EBX [8..15] * 8

movzx eax,bh

shl eax,3

.ok:

pop ebx

ret

endp

Результат, разумеется, в EAX.

Vyacheslav

Vyacheslav

xk8.ru/inteldoc

Третий (вроде) том.

Столько новой инфы мне минимум на пару месяцев хватит. Давно асмом не занимался. Спасибо

Anonymous

Anonymous

А вот такой вопрос - если я заюзал y некоторый ISA а при выполнении мне линукс пишет Illegal Instruction

А вот такой вопрос - если я заюзал y некоторый ISA а при выполнении мне линукс пишет Illegal Instruction

А где ты мать с ISA нашёл?

Anonymous

Anonymous

Вот я и спрашиваю, важно чтобы версия ядра была актуальная, чтобы собранное приложение запустить или нет

Vyacheslav

Vyacheslav

Вот я и спрашиваю, важно чтобы версия ядра была актуальная, чтобы собранное приложение запустить или нет

Может быть важно из-за обновлений микрокода. С какой-то версии их из ядра в пакет отдельный вынесли.

Хм. То есть если пересобрать ядро с новым микрокодом, то может хватить?

Какое ядро? В 3.х уже было в отдельном пакете.

Anonymous

Anonymous

400751: fd ff ff

400754: 62 f2 75 48 52 (bad)

400759: c2 62 f1 retq $0xf162

...

4007f0: 62 f2 f5 48 b5 c2 vpmadd52huq %zmm2,%zmm1,%zmm0

4007f6: 62 f1 7c 48 11 85 50 vmovups %zmm0,-0xb0(%rbp)

Eugene

Eugene

Если cpuid показывает, что инструкция не поддерживается, значит её не поддерживает процессор. ОС тут ни причём вообще. Если только это не привилегированная инструкция. Но vpmadd* - это обычная инструкции AVX512, vmovups - это AVX-1.

Проц какой?

Eugene

Eugene

Вторая инструкция в objdump правильно распознается

Вторая инструкция - это часть первой, vpdpwssd длиннее 5 -ти байт.

bilka00

bilka00

ඞ

ඞ